专用集成电路设计与软件开发的界定 技术、流程与应用的差异辨析

专用集成电路(ASIC,Application-Specific Integrated Circuit)设计和软件开发虽然同属信息技术领域,服务于系统实现与性能优化,但在本质、方法、工具和应用层面存在显著差异。明确界定二者,有助于理解硬件与软件协同工作的现代计算体系。以下从多个维度进行辨析。

一、本质与目标差异

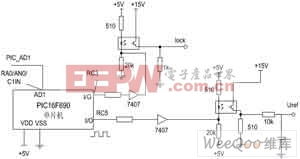

专用集成电路设计的本质是硬件实现。其目标是根据特定应用需求(如高速数据处理、低功耗运行),设计并制造出物理的集成电路芯片。它涉及晶体管级或逻辑门级的电路设计,最终产出的是硅片上的实体硬件,具有固定功能、高性能和高能效比的特点,但一旦制造完成,功能通常无法更改(全定制ASIC),或仅有有限可编程性(如FPGA作为ASIC原型或半定制方案)。

软件开发的本质是逻辑实现。其目标是通过编写代码,在通用计算平台(如CPU、GPU)上创建可执行的程序或系统。软件是存储在存储器中的指令序列,依赖底层硬件执行,产出的是代码、可执行文件或服务。软件具有高度灵活性,可通过更新轻松修改功能,但性能受限于运行平台的硬件架构。

二、设计流程与工具差异

ASIC设计流程复杂且周期长,涉及多个阶段:

1. 系统规范:明确芯片功能、性能、功耗和物理指标。

2. 架构设计:确定模块划分、总线结构等。

3. RTL设计:使用硬件描述语言(如Verilog、VHDL)描述电路行为。

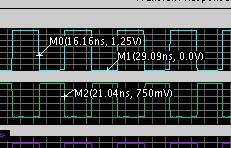

4. 验证:通过仿真、形式验证确保逻辑正确性。

5. 逻辑综合:将RTL转换为门级网表。

6. 物理设计:包括布局布线、时序分析、功耗优化等。

7. 制造与测试:交付晶圆厂流片,并进行硅后测试。

工具链包括Cadence、Synopsys等EDA(电子设计自动化)工具,强调时序、面积、功耗的物理约束。

软件开发流程相对灵活,常见阶段包括:

1. 需求分析:确定软件功能与用户需求。

2. 设计:进行系统架构、模块设计。

3. 编码:使用高级语言(如C++、Python)实现。

4. 测试:单元测试、集成测试等。

5. 部署与维护:发布版本并持续更新。

工具链包括IDE、编译器、调试器、版本控制系统等,注重代码效率、可维护性和跨平台兼容性。

三、技术栈与技能要求差异

ASIC设计需要硬件专业知识:

- 熟悉数字电路基础、半导体物理。

- 掌握硬件描述语言和EDA工具。

- 了解制造工艺、信号完整性等。

- 技能更偏向电气工程和微电子领域。

软件开发需要软件工程知识:

- 精通编程语言、算法与数据结构。

- 熟悉操作系统、数据库、网络协议。

- 掌握软件工程方法和团队协作工具。

- 技能更偏向计算机科学和信息技术。

四、应用场景与成本差异

ASIC设计适用于:

- 高性能计算(如AI加速芯片、矿机)。

- 嵌入式系统(如手机SoC、物联网设备)。

- 对功耗、体积、速度有严苛要求的场景(如航天、汽车电子)。

成本高昂,涉及流片费用(可达数百万美元),适合大批量生产以均摊成本。

软件开发适用于:

- 通用计算平台上的应用程序(如移动App、Web服务)。

- 算法仿真、系统控制、数据分析等。

- 快速迭代和功能更新的场景。

初始成本较低,但维护和升级可能持续投入。

五、协同与融合趋势

尽管存在差异,二者在现代系统中紧密协同:

- 软硬件协同设计:如ASIC需配套驱动程序、固件,通过软件发挥硬件潜能。

- 高层次综合(HLS):允许用C/C++等软件语言描述硬件功能,模糊了部分边界。

- 异构计算:CPU、GPU、ASIC(如TPU)共同工作,由软件调度任务。

###

界定专用集成电路设计与软件开发,核心在于区分“物理硬件实现”与“逻辑指令实现”。ASIC设计追求在硅片上固化高效功能,关注物理约束;软件开发追求在通用硬件上灵活执行,关注逻辑抽象。二者相辅相成,共同推动从智能设备到数据中心的技术演进。理解其差异,有助于在系统设计中做出合理的技术选型与资源分配。

如若转载,请注明出处:http://www.6shuju.com/product/45.html

更新时间:2026-04-18 23:33:23