集成电路制造工艺与可制造性设计的软件开发融合

集成电路(IC)作为现代信息技术的核心,其制造工艺日益复杂,涉及数百道精密步骤。随着工艺节点不断缩小至纳米级,物理极限和制造成本带来的挑战愈发严峻。在此背景下,可制造性设计(Design for Manufacturing, DFM)应运而生,成为连接芯片设计与实际制造的关键桥梁。而支持DFM理念落地的各类软件开发,则扮演着至关重要的角色。

集成电路制造工艺通常包括硅片制备、薄膜沉积、光刻、刻蚀、离子注入、化学机械抛光(CMP)以及封装测试等一系列复杂工序。尤其是进入先进制程(如7纳米、5纳米及以下)后,制造过程中出现的工艺波动、版图图形失真、化学机械抛光不均匀性等问题会显著影响芯片的最终性能、良率和可靠性。这些问题无法再通过传统的设计规则检查(DRC)和版图与电路图一致性检查(LVS)完全规避,因此,DFM方法论变得至关重要。

可制造性设计(DFM)是一套在设计阶段就预先考虑并规避制造中可能遇到问题的设计理念和方法学。其核心目标是提高设计的工艺窗口,从而提升芯片的制造良率、可靠性并控制成本。DFM涉及多个层面:在器件层面,需要考虑工艺波动对晶体管阈值电压等参数的影响;在互连线层面,需关注铜互连的化学机械抛光均匀性、通孔与金属线的覆盖率等;在系统层面,则需评估热效应、电迁移等可靠性问题。

推动DFM有效实施的引擎,正是一系列专业的EDA(电子设计自动化)软件和制造相关软件。这些软件开发构成了一个庞大的技术生态系统:

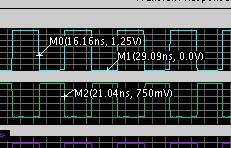

- 建模与仿真软件:这类软件用于建立精确的工艺模型和器件模型。例如,TCAD(工艺与器件仿真)软件可以虚拟模拟整个制造工艺流程,预测工艺偏差对器件电学特性的影响,为设计端提供关键参数。光刻仿真软件(如计算光刻软件)则能模拟光刻过程,预测版图图形在光刻后的形貌,并提前发现可能出现的分辨率不足、线端缩短等热点(Hot Spot),从而指导设计修正或生成辅助图形(OPC、SRAF)。

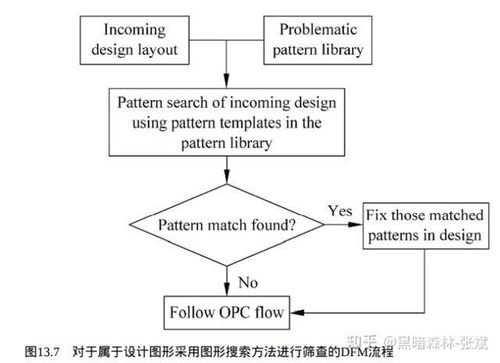

- 分析与优化工具:在物理设计阶段,DFM软件被深度集成到设计流程中。它们可以对设计版图进行可制造性分析,识别出对工艺波动敏感的区域(如密度不均匀、线宽/线距临界、通孔阵列等),并提供自动或手动的优化建议。例如,金属填充工具可以自动添加虚设金属图形,以改善化学机械抛光的均匀性;布线工具则集成了基于良率考虑的布线算法,避免产生难以制造的图形。

- 良率分析与学习系统:芯片制造完成后,通过测试和失效分析获得的海量良率数据需要被有效利用。相关的数据分析软件运用机器学习、大数据分析等技术,从测试数据、晶圆图(Wafer Map)和失效芯片的物理分析结果中,挖掘出影响良率的关键设计特征或工艺步骤,形成“良率学习循环”。这些知识被反馈给设计团队,用于改进下一代产品的DFM策略,甚至直接生成设计规则或版图优化规则库。

- 设计-制造协同平台:随着设计与制造的界限变得模糊,协同平台软件变得日益重要。它们旨在安全、高效地共享必要的设计数据(如抽象化的版图特征)和制造数据(如工艺能力指标),打破“信息墙”,使设计者在早期就能基于实际的工艺能力进行设计决策,实现真正的“设计即正确”(Right-First-Time Design)。

集成电路制造工艺将继续向更细微、三维集成(如3D IC、GAA晶体管)方向发展,新材料和新工艺将不断引入。这将对可制造性设计及其软件开发提出更高要求:软件需要处理更复杂的物理效应(如量子效应)、更海量的数据,并更深度地融合人工智能技术,实现从“发现问题-解决问题”到“预测问题-预防问题”的智能化跨越。软硬件协同优化、芯片-封装-系统级协同DFM也将成为重要趋势。

总而言之,集成电路制造工艺的进步,不断驱动着可制造性设计理念的演进,而后者又催生了对更强大、更智能的软件工具的迫切需求。这三者——精密工艺、设计方法论和软件工具——构成了一个紧密联动、相互促进的三角关系,共同推动着芯片产业持续突破物理与经济的极限,为数字时代的创新发展奠定基石。

如若转载,请注明出处:http://www.6shuju.com/product/51.html

更新时间:2026-04-18 00:42:02